ARM学习(23)AMP和SMP的认识与理解

笔者来聊聊AMP和SMP架构理解(多核下系统)。

1、简介介绍

笔者经常听到ARM架构时,谈到SMP的架构或者AMP的架构,今天特意来了解一下,主要是针对多core处理,对于常见的MCU应用场景,可以比较少,往往是需要较强的性能或者应付复杂的场景,会碰到多核的场景。

- SMP:Symmetric multiprocessing,对称多处理器

- AMP:ASymmetric multiprocessing,非对称处理器

故名思意,

- 对称处理器,其结构上是相同的,比如架构的一些特性,核的架构,指令集,以及内存空间等,

- 非对称处理器,往往每个core都有特殊的地址,比如地址空间不同,又比如core的架构不同,指令集不同,运行的OS也不同,所以,往往都是独立编译,而SMP是统一编译,则一个elf文件,而AMP则是每个core一个elf文件。

2、对称处理器 SMP

主要Core的运行方式特点有如下:

- 运行的指令集相同,架构相同

- 运行的OS相同

- 使用项目的内存空间和地址映射

- 共享相同的地址空间(物理以及虚拟)

- 符号表相同

-

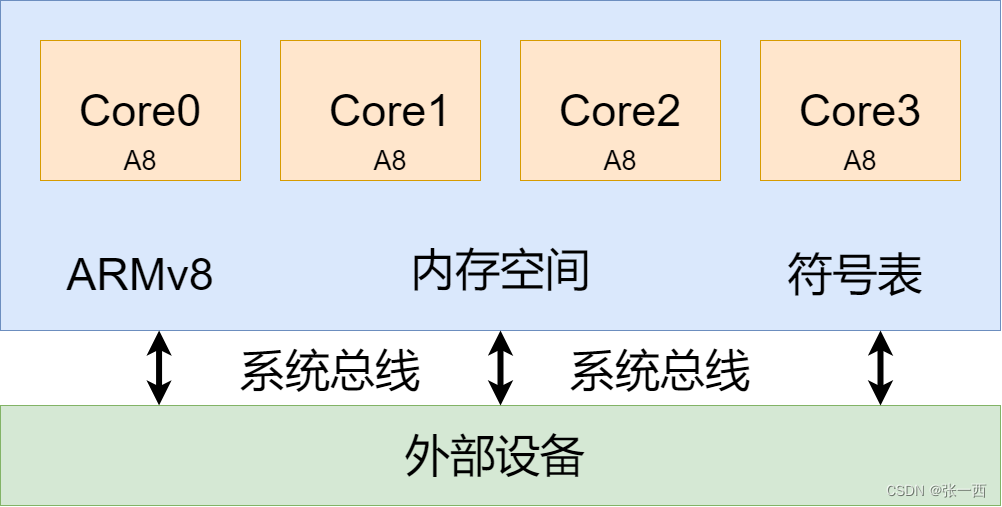

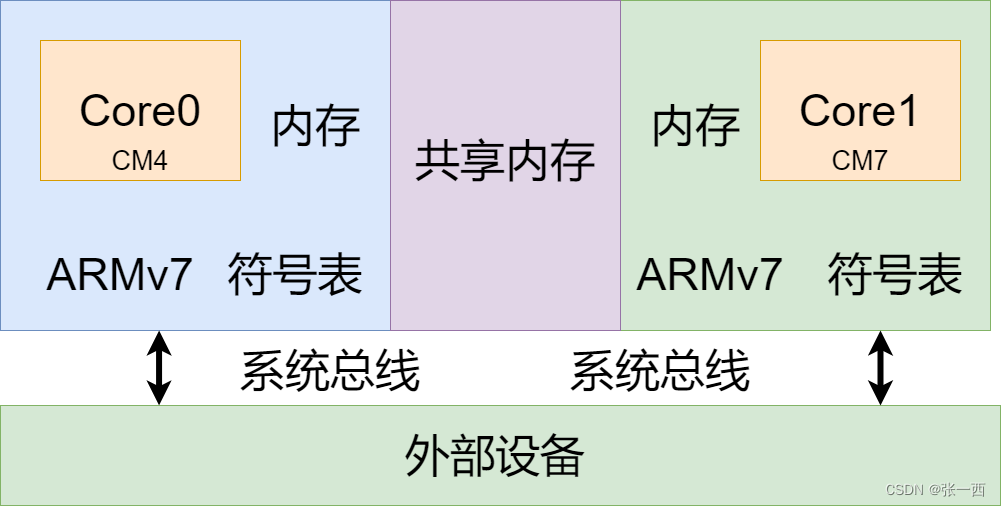

上图绘制了一个SMP的示例图,其每个core的内存空间相同,都可以访问程序中的每个函数,即符号表是共享的,那么OS则也是运行的相同的,指令集是相同的。

-

内存空间相同,每个core看到的地址和函数都是一样的地址,比如使用指针函数获取地址时,获取同一个函数地址都是相同的,也可以正常执行, 如果地址空间不同,则需要注意,不能直接获取地址执行。

-

再来说说符号表,ARM学习(7) symbol 符号表以及调试,笔者之前介绍过一次,就是所有的符号都可以搜索到,可以正常编译,主要就是(全局变量,函数,链接器生成的一些符号等)

-

指令集就不做过多介绍,ARM学习(6) 指令集学习,这个可能体现的不那么明显,用户往往看不到,看汇编指令或者异常架构时会学习到这个,比如启动,中断向量表等。

-

栈和core内的cache就不多说了,肯定是各自独立的,当然也有共享的cache,比如L2 L3这种cache

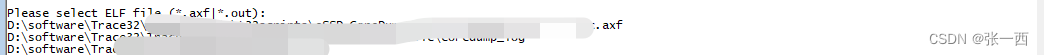

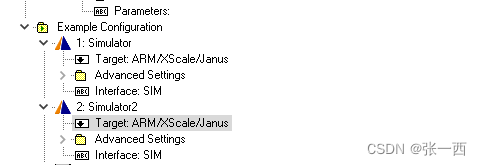

Trace32加载时,选择一个elf文件即可,可以同时看到多个core的寄存器信息(寄存器这些数量等都是相同的),包括当前Pc的位置等

可以随便切换core,看到其他core在执行函数的位置。

3、 非对称处理器 AMP

主要Core的运行方式特点有如下:

- 运行的指令集或者架构不同

- 运行的OS不同

- 拥有不同的内存空间和地址映射

- 拥有各自的地址空间(物理和虚拟)

- 符号表信息不同

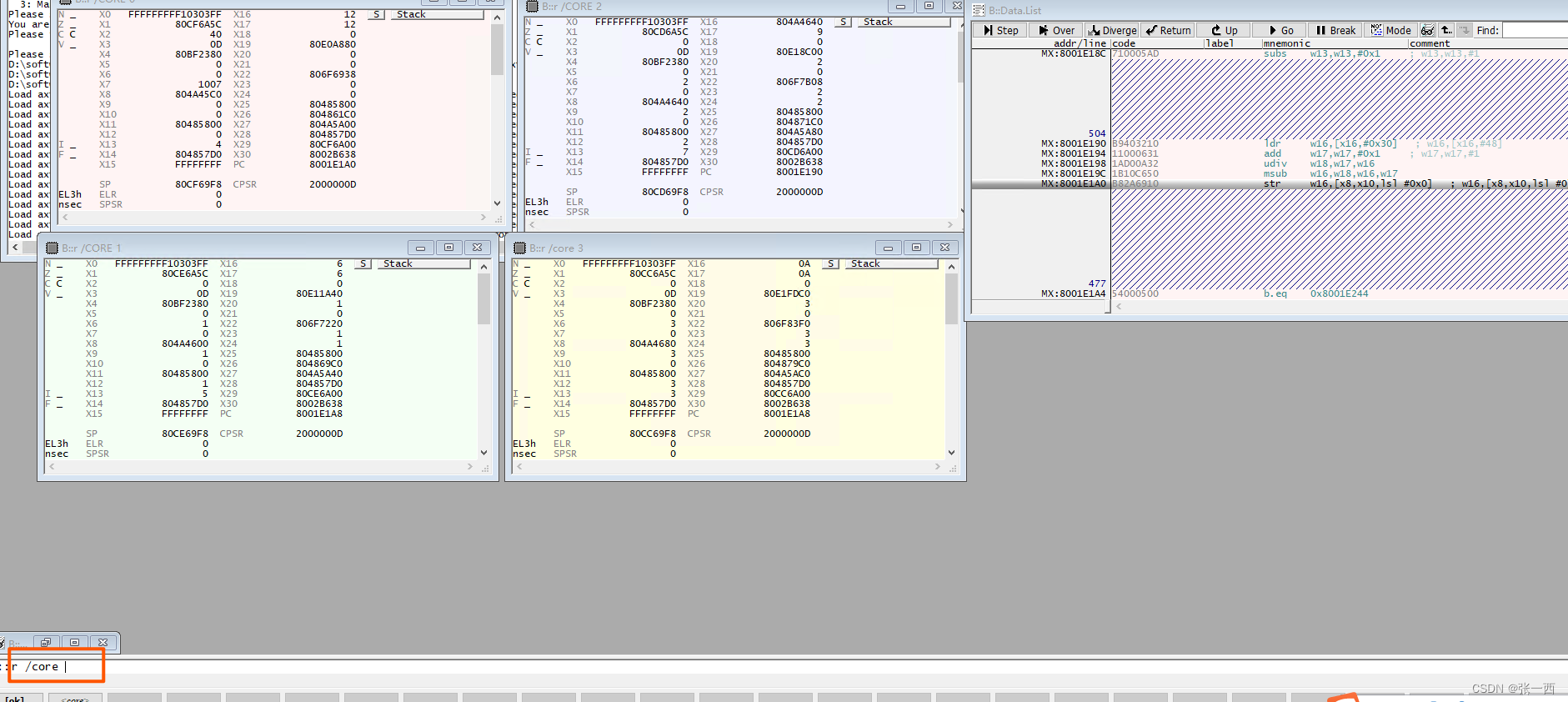

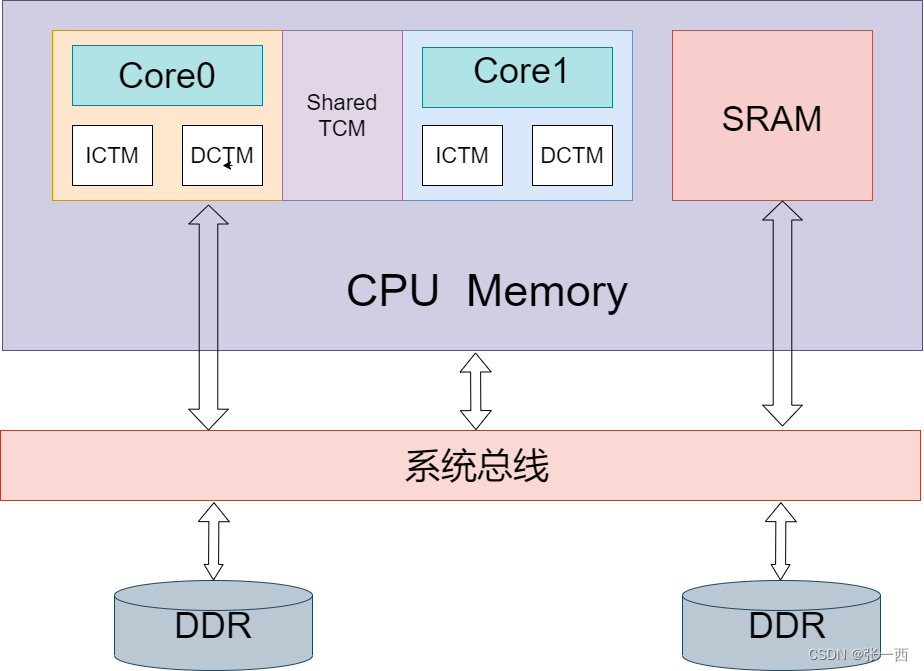

再来看看AMP的架构,core之间的内存空间独立,架构或者指令集可能不一样,符号表都是属于各自的,通信可以通过共享的内存进行通信,但是通信的地址和外部设备的地址可能不同,也可能相同。

-

core之间地址独立,意思可能双core的地址空间独立编址,比如有部分空间都是从0地址开始,所以地址即无法访问对方的空间,这也不是完全绝对的,有些地址空间也可以通过总线映射,让对方访问,不过各自的core在自己的视野里看到对方的core的地址会不同。

-

elf文件各自独立,即需要两次编译 两次链接形成各自的可执行文件,所以相关的宏以及符号表都会有所不同,当然运行的OS也会不同,

-

地址不同,带来的编程方式也不同,各自core视野地址不同,则无法使用地址来进行内存空间访问。

Trace32 需要开启两个窗口分别进行debug,然后分别选择对应core的elf文件。

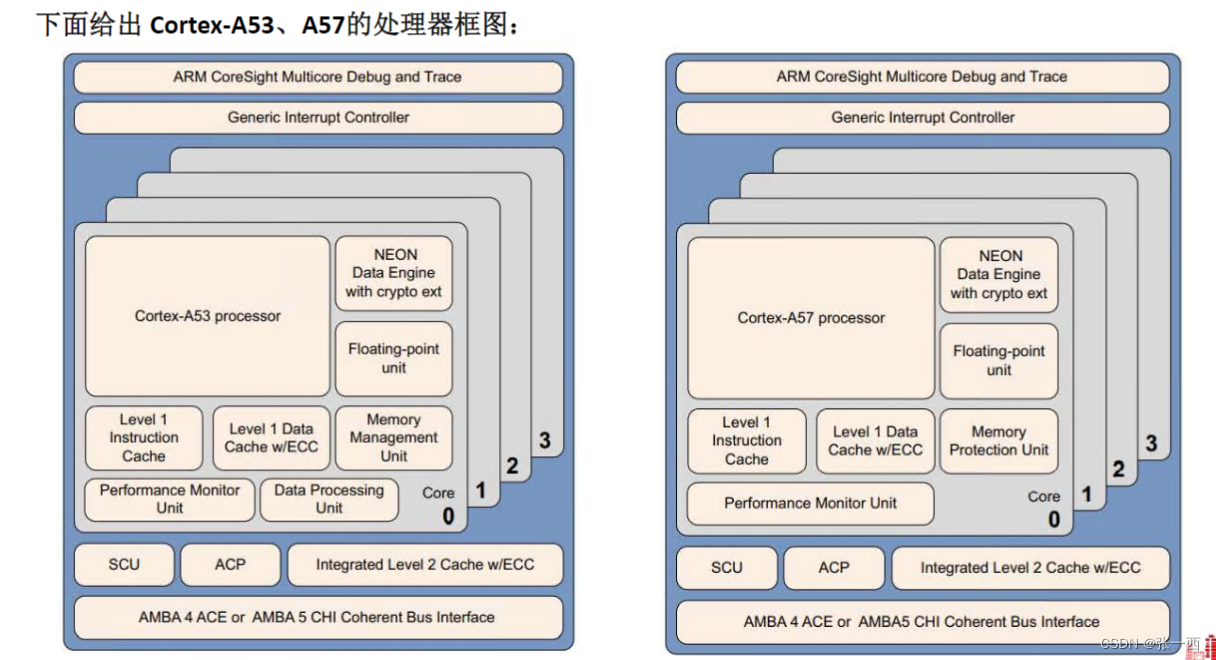

4、实际芯片架构

-

AMP 双core Cortex-R5的架构芯片

-

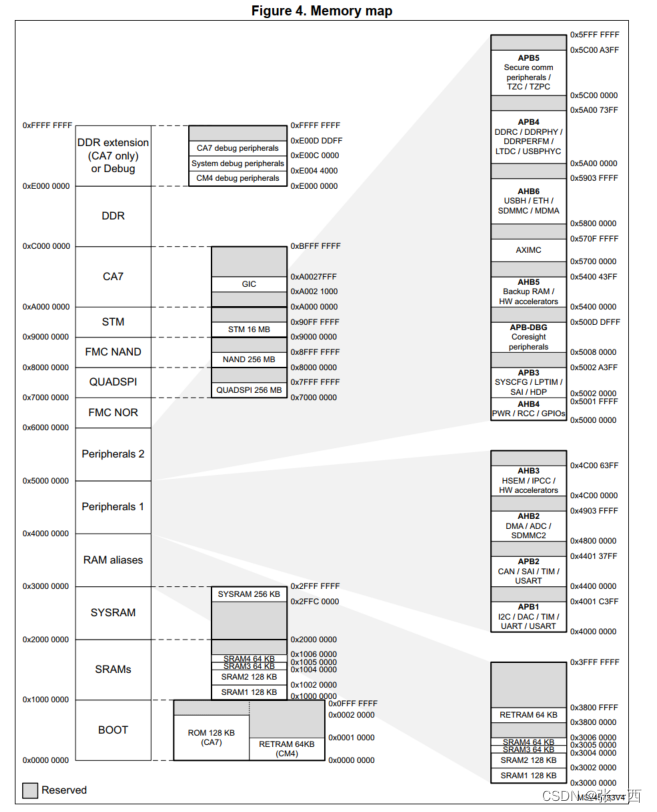

AMP STM32MP153 (dual CortexA7 + CortexM4)

-

SMP 6core的Cortex-A53架构芯片

版权声明:

作者:ZhangYixi

链接:http://zyixi.xyz/arm%e5%ad%a6%e4%b9%a0%ef%bc%8823%ef%bc%89amp%e5%92%8csmp%e7%9a%84%e8%ae%a4%e8%af%86%e4%b8%8e%e7%90%86%e8%a7%a3/

来源:一西站点

文章版权归作者所有,未经允许请勿转载。

共有 0 条评论