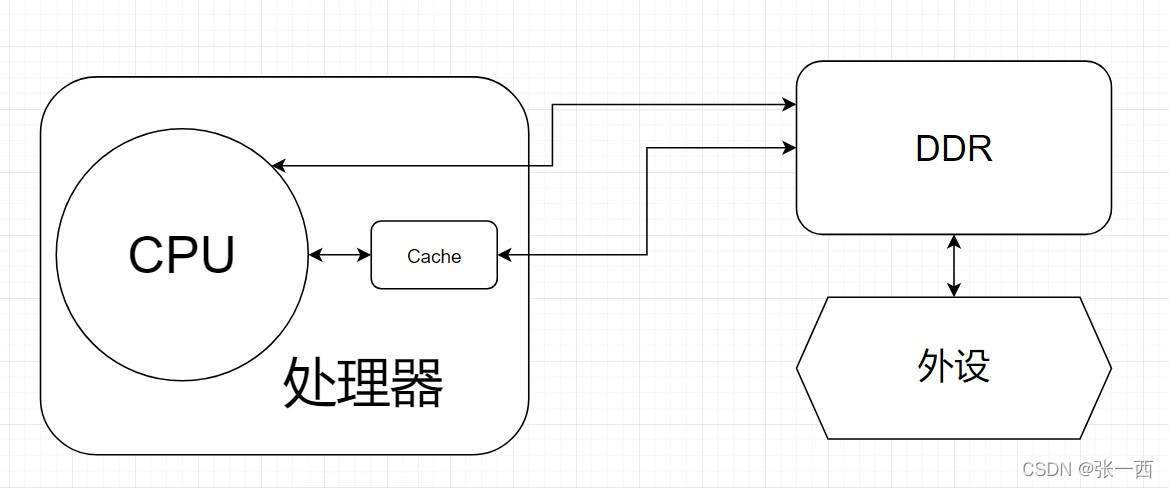

CPU、Cache以及DDR之间访问关系

笔者介绍一下CPU、Cache及DDR之间的数据流向。

俗话说,开局一张图,下面全靠讲。

Cache是一个介于CPU以及DDR(DRAM)之间的一个高速缓存(一般好像是SRAM),在处理器内部,读写速度较DDR高,但是低于CPU的速度。假如没有Cache,直接访问DDR,CPU的速度远远高于DDR,那么CPU就需要等待DDR的数据到来,才能做其他事情,就会造成CPU使用效率较低。

使用Cache之后,提前将DDR的数据缓存到Cache中,如果恰好CPU访问DDR的数据在Cache中有,那么CPU拿到数据的时间将更短,处理效率将大大增加。如何提高Cache的命中率那是另外一回事,不在本文的讨论中。

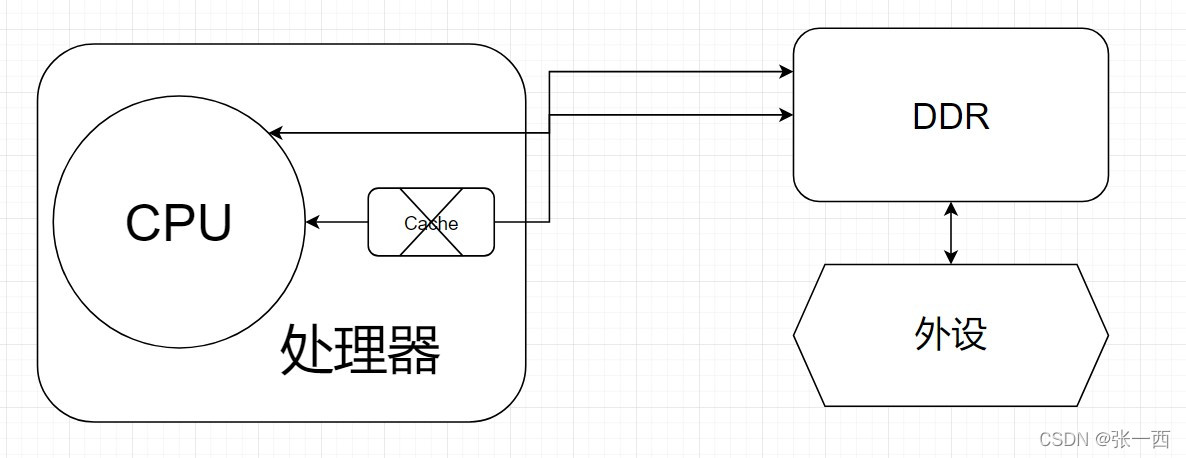

但是同时也会造成一致性问题,即CPU的访问的数据(Cache)与DDR的数据没有同步,造成执行错误。

假设一种真实情况,CPU要访问DDR中的一块数据,那么这块数据会放在Cache中,之后DMA控制器直接将外设的数据放在DDR中,更新了刚刚的那一块CPU要访问的数据,此时CPU要获取数据进行处理,还是拿着Cache中未更新的数据,就会造成一致性问题。

如何避免这种问题呢?将Cache中的数据清空,或者将DDR与Cache的数据同步,即可解决一致性问题,所以在使用外设的时候,假如有Cache的话,一定要注意这个问题。

版权声明:

作者:ZhangYixi

链接:http://zyixi.xyz/cpu%e3%80%81cache%e4%bb%a5%e5%8f%8addr%e4%b9%8b%e9%97%b4%e8%ae%bf%e9%97%ae%e5%85%b3%e7%b3%bb/

来源:一西站点

文章版权归作者所有,未经允许请勿转载。

共有 0 条评论